Capacitores de DesacoploEs sabido que los circuitos digitales requieren capacitores de desacoplo en la fuente de poder. Si se examina la tarjeta madre de un PC, se verá que existen varios capacitores conectados entre fuente y tierra, en paralelo unos con otros. En esta nota se explica porqué se requieren dichos capacitores, porqué no se pueden sustituir por uno de mayor capacidad y qué criterios deben usarse para colocarlos en un circuito. Como se verá, la ausencia de los capacitores de desacoplo, o la ubicación incorrecta de ellos, puede provocar un funcionamiento errático del circuito. Las causas del funcionamiento errático son:

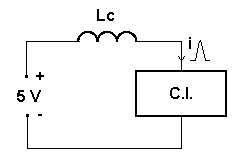

En la figura 1 se muestra un modelo simplificado del mecanismo que genera el problema. Lc representa la inductancia parásita del cable que conecta la fuente al circuito integrado C.I.

Figura 1: Circuito simplificado sin capacitor de desacoplo Para estimar la magnitud de la fluctuación en el voltaje de polarización del C.I. se supondrá que circula un pulso de corriente de forma triangular (ver figura 1) con una amplitud de 50 mA y un ancho total de 10 nseg, que corresponde al tiempo de conmutación de familias lógicas comunes. Este pulso puede ser ocasionado por consumo interno del C.I. durante la conmutación, o puede ser requerido para cargar capacidades parásitas conectadas a una o más líneas de salida que conmutan de 0 a 5 V. De hecho, si se calcula la carga eléctrica asociada al pulso, equivalente al área bajo la forma de onda de la corriente, se obtiene: q = 50 mA · 10 nseg / 2 = 250·10-12 C Esa es la carga requerida para producir un cambio de 5 V en un capacitor de C = q / v = 250·10-12 / 5 = 50 pF Una capacidad parásita de 50 pF es perfectamente posible en un protoboard. Por lo tanto, basta una capacidad parásita normal para forzar la circulación de un pulso de corriente tal como el supuesto. El pulso de corriente tiene una di/dt de magnitud 50 mA / 5 nseg = 10·106 Amp/seg (10 millones de Amperes por segundo) La inductancia de un conductor delgado de 10 cm de largo es del orden de 0.1 µH. La magnitud del voltaje originado en el inductor por el pulso de corriente es: v = L · di/dt = 0.1·10-6 · 10·106 = 1 V Ese voltaje se resta a la tensión de la fuente cuando la corriente aumenta, y se suma cuando la corriente disminuye, haciendo que la tensión de alimentación del C.I. fluctúe entre 4 y 6 V, excediendo la tolerancia permitida, que generalmente es del 5 %, o 0.25 V. Como los datos asumidos en el cálculo anterior son -en buena medida- arbitrarios, no existe ninguna seguridad respecto de la magnitud de la fluctuación, la cual podría ser menor o mayor, dependiendo de la velocidad de cambio de la corriente y de la inductancia del cable. Lo importante no es el valor preciso obtenido (1 V), sino el hecho de que es una fracción significativa de la tensión de alimentación, por lo que podría alterar la información almacenada en los flip-flop del circuito, generando un funcionamiento errático. Resulta imposible para la fuente de poder evitar la fluctuación de voltaje calculada anteriormente, ya que ésta puede aparecer en sólo algunos centímetros de cable. Sin embargo, los capacitores de desacoplo ubicados cerca de los C.I. pueden reducir significativamente las fluctuaciones. Los capacitores actúan como depósitos de carga eléctrica, que se descargan en una pequeña proporción cuando entregan el pulso de corriente, y se recargan luego en un intervalo de tiempo mayor. Ver figura 2.

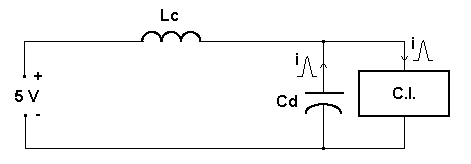

Figura 2: Capacitor de desacoplo Cd ubicado cerca del circuito integrado Para estimar Cd, se puede asumir que se permite una fluctuación de 0.01 V en la tensión de alimentación del C.I. cuando circula el pulso de corriente antes supuesto. Entonces: Cd = q / v = 250·10-12 / 0.01 = 25 kpF En la práctica se utilizan capacitores de desacoplo de 10 a 100 kpF. Si bien algunos circuitos digitales pueden funcionar correctamente sin capacitores de desacoplo, al no colocarlos se asume un riesgo innecesario, ya que se pueden generar fallas cuyo origen resulta difícil de pesquisar. Por ejemplo, los programas de los microcontroladores pueden ejecutarse en forma incorrecta, creando la impresión de que existe una falla en la lógica del programa, cuando en realidad se trata de un problema en el hardware.

Conclusión: los circuitos digitales debieran incluir al menos un capacitor de desacoplo de entre 10 y 100 kpF ubicado cerca de cada C.I. Juan Vignolo Barchiesi Enero de 2008 |

No todos los capacitores físicos son adecuados para

desacoplo de circuitos digitales. Algunos capacitores (tales

como los electrolíticos o de tantalio) contienen una

inductancia residual que debilita el efecto

de desacoplo en frecuencias altas, pero son adecuados para

reducir ripple y ruido de baja frecuencia. Los

No todos los capacitores físicos son adecuados para

desacoplo de circuitos digitales. Algunos capacitores (tales

como los electrolíticos o de tantalio) contienen una

inductancia residual que debilita el efecto

de desacoplo en frecuencias altas, pero son adecuados para

reducir ripple y ruido de baja frecuencia. Los